# HIGHPOINT TECHNOLOGIES,INC. HPT366 DATA MANUAL

The products described in this publication are products of HighPoint Technologies.

Copyright 1999 By HighPoint Technologies, Inc. All Rights Reserved Printed in U.S.A.

#### **Preface**

This manual assumes some prior knowledge of current and information of HPT366 Standard.

The data manual organized into the following chapter :

Chapter 1- Overview,

Chapter 2- Signal Description,

Chapter 3- Registers.

Chapter 4- Electrical Parameters,

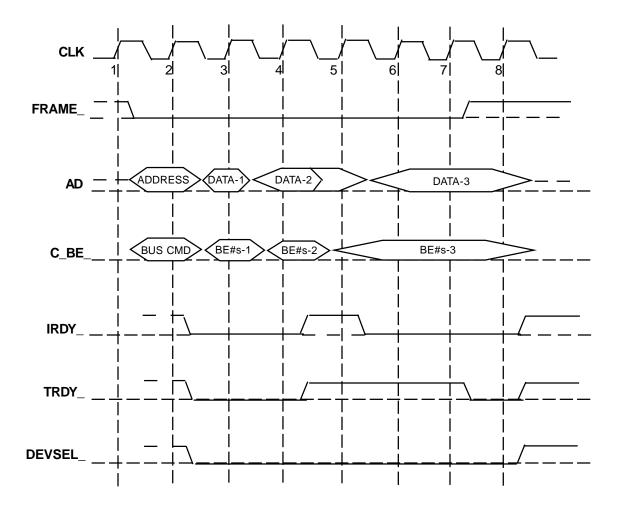

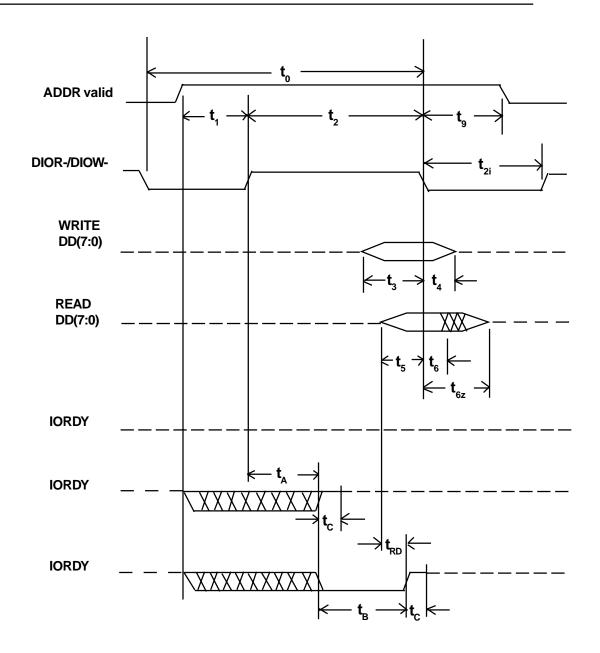

Chapter 5-Timing,

Appendix A- Mechanical Dimensions.

Appendix B- Diagrams.

Please give us your advice after you read it.

## **Table of Contents**

| Chapter 1                        |            |

|----------------------------------|------------|

| Overview                         |            |

| Introduction                     | 1.1        |

| 1.1 HPT366 Block Diagram         |            |

| 1.2 Features                     |            |

| 1.2 realures                     | 1-3        |

|                                  |            |

|                                  |            |

|                                  |            |

| Oh and an O                      |            |

| Chapter 2                        |            |

| Signal Description               |            |

| Introduction Pins                | 2-1        |

| 2.1 128 Pins Signal Description  |            |

| 2.2 144 Pins Signal Description  |            |

| 2.3 128 Pins Listing             |            |

| System Pins                      |            |

| Power and Ground Pins            |            |

| Interface Control Pins           |            |

| Arbitration Pins                 |            |

| PCI Interrupt Pins               |            |

| Address/Data Pins                |            |

| IDE Interrupt Pins               |            |

| EPROM Interface Pins             |            |

| Other Pins                       |            |

| 2.4 144 Pins Listing             |            |

|                                  |            |

|                                  |            |

|                                  |            |

|                                  |            |

|                                  |            |

| Chapter 3                        |            |

|                                  |            |

| Registers                        | 3-1        |

| Introduction                     |            |

| 3.1 Registers Listing            |            |

| 3.2 PCI Configuration Registers  |            |

| Vendor ID and Device ID          |            |

| Command Register                 |            |

| Status Register                  |            |

| Revision Identification Register |            |

| Class Code Register              |            |

| Latency Timer Register           |            |

| Header Type Register             | 3-7<br>2-7 |

|                                  |            |

| Control Block Register                                                                                                                                            | 3-8               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| I/O Space Base Register                                                                                                                                           | 3-8               |

| CardBus CIS Pointer Register                                                                                                                                      | 3-8               |

| Subsystem Vendor ID Register                                                                                                                                      | 3-9               |

| Subsystem ID Register                                                                                                                                             | 3-9               |

| Expansion ROM Base Register                                                                                                                                       | 3-9               |

| Interrupt Line Register                                                                                                                                           | 3-10              |

| Interrupt Pin Register                                                                                                                                            | 3-10              |

| IDE Timing 0 Register                                                                                                                                             | 3-11              |

| IDE Timing1 Register                                                                                                                                              | 3-12              |

| MISC. Control1 Register                                                                                                                                           | 3-13              |

| MISC. Control2 Register                                                                                                                                           | 3-14              |

| MISC. Control3 Register                                                                                                                                           | 3-15              |

| MISC. Control4 Register                                                                                                                                           | 3-15              |

| Bus Status1 Register                                                                                                                                              | 3-16              |

| Bus Status2 Register                                                                                                                                              | 3-17              |

| Cable Select Register                                                                                                                                             | 3-17              |

| 3.3 I/O Space Registers                                                                                                                                           | 3-18              |

| Bus Master Command Register                                                                                                                                       | 3-18              |

| Bus Master Status Register                                                                                                                                        | 3-18              |

| Bus Master Scatter Gather Table Base Register                                                                                                                     | 3-19              |

|                                                                                                                                                                   |                   |

| Chapter 4                                                                                                                                                         |                   |

| Chapter 4 Electrical Parameters                                                                                                                                   |                   |

| Electrical Parameters                                                                                                                                             | 4-1               |

| Electrical Parameters Introduction                                                                                                                                |                   |

| Electrical Parameters Introduction                                                                                                                                | 4-1               |

| Electrical Parameters Introduction                                                                                                                                | 4-1<br>4-2        |

| Electrical Parameters Introduction                                                                                                                                | 4-1<br>4-2<br>4-3 |

| Electrical Parameters Introduction                                                                                                                                | 4-1<br>4-2<br>4-3 |

| Electrical Parameters Introduction                                                                                                                                |                   |

| Electrical Parameters Introduction 4.1 3.3V Signaling Environment DC Specifications AC Specifications  Timing Introduction 5.1 Timing Parameters 5.2 Clock Timing |                   |

| Electrical Parameters Introduction                                                                                                                                |                   |

| Electrical Parameters Introduction 4.1 3.3V Signaling Environment DC Specifications AC Specifications  Timing Introduction 5.1 Timing Parameters 5.2 Clock Timing |                   |

| Appendix A | A | pi | pe | n | cik | <b>( A</b> |

|------------|---|----|----|---|-----|------------|

|------------|---|----|----|---|-----|------------|

| Mechan | ical | Dimei | nsions |

|--------|------|-------|--------|

| Introduction       | A-1 |

|--------------------|-----|

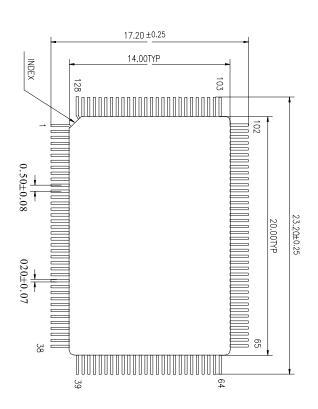

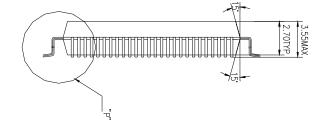

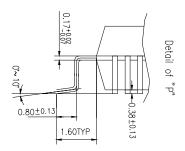

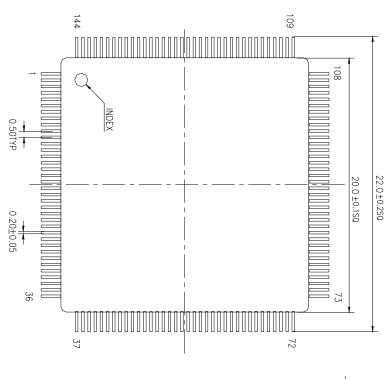

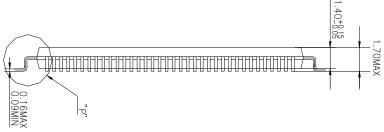

| A.1 128 Pins SQFP  | A-2 |

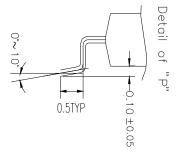

| A 2 144 Pins I OFP | A-3 |

# Appendix B

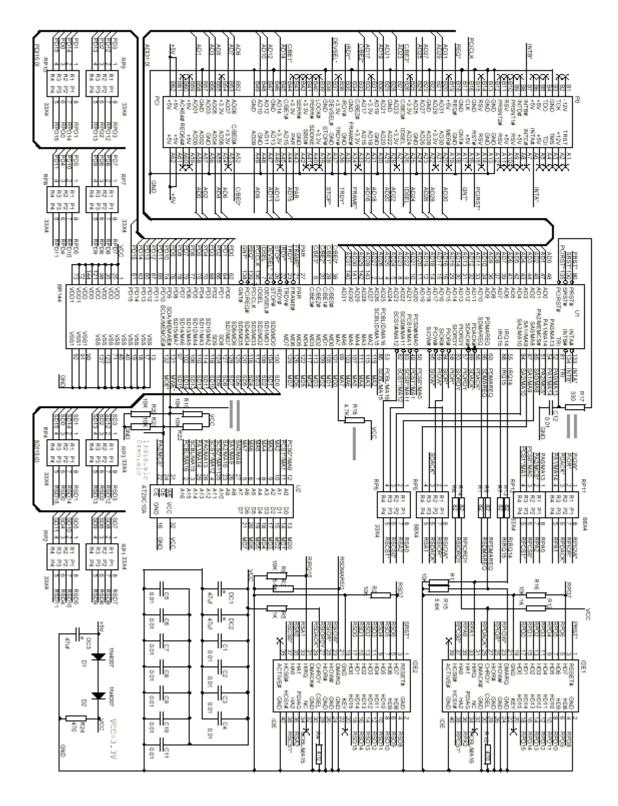

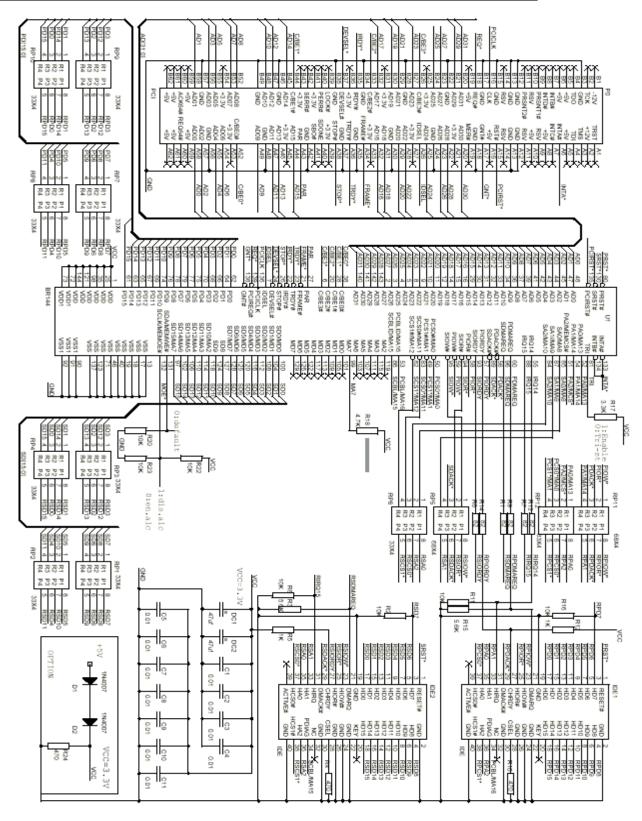

#### Diagrams

| Introduction                             | B-' |

|------------------------------------------|-----|

| B.1 Schematic Diagrams For Add-On Card   | B-: |

| B.2 Layout For Add-On Card               |     |

| B 3 Schematic Diagrams For Main Board B- |     |

# Chapter 1 Overview

## Introduction

This chapter will combines information and features for the HPT366. HPT366 has been designed to let you add additional high performance device(s) to your current computer system.

1-1

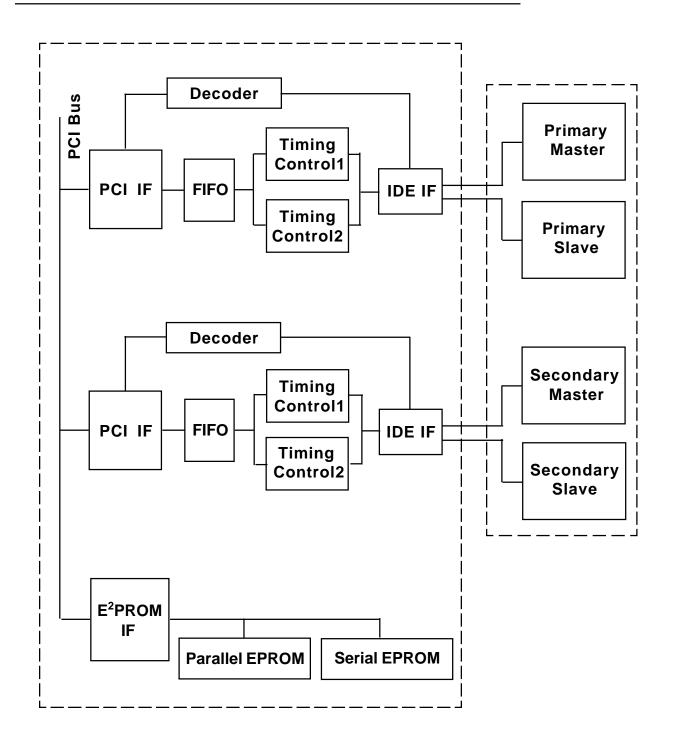

## 1.1 Block Diagram

#### 1.2 Features List

There are two packages. One is 128 Pin, the other is 144 Pin.

- Ultra DMA 66MB/s operation.

- Two PCI functions in a single chip.

- Two independent ATA channels (one channel per PCI function).

- Dedicated ATA Bus

- 256 Byte FIFO per ATA channel.

- Large FIFO independent

- Supports all ATAPI CD-ROM, DVD-ROM, CD-R, CD-RW, LS-120, Tape and ZIP devices.

- Easy Plug-and-Play feature.

- Supports up to 4 devices IDE devices. (Coexist with on-board IDE)

- Supports Hard Drive capacity large than 8.4 GB.

- Supports MS-DOS, Windows 3.x, Windows 95, Windows 98, Windows NT, OS2 WARP, Novell Netware and SCO UNIX.

- Supports booting function with Flash Memory interface.

- Automatically fine tunes to the best performance for each individual IDE/ATAPI device.

- Backward Compatible

- Concurrent PIO and bus master access (ATA port accessible during DMA transfer).

- Total ATA bus tri-state by external control and Supports Hotswap (Low signal Current)

- Reloadable PCI configuration using parallel EPROM or 2 wire serial EPROM.

- (Loading address 0 for serial size EPROM, loading address 1000H for parallel EPROM.)

- 128 Pin SQFP (Parallel EPROM IF (Interface) share with ATA channels, or independent serial EPROM).

- 144 Pin LQFP(Dedicated Parallel EPROM pins).

- Small foot print 144 pin LQFP

- Up to 44MHz PCI bus Clock.

- Multifunction

- Embed serial resistor on chip for ATA spec.

## **Chapter 2 Signal Description**

#### **Introduction Pins**

This chapter will introduction all pins for you.

The interface signals are organized into the following functional groups:

- \* System Pins,

- \* Power and Ground Pins,

- \* Interface Control Pins,

- \* Arbitration Pins,

- \* PCI Interrupt Pins,

- \* Address/Data Pins,

- \* IDE Interface Pins,

- \* EPROM Interface Pins,

- \* Other Pins.

There are three signal type definitions:

- I Input, a standard input-only signal.

O Totem Pole Output, a standard output driver.

I/O Input and Output.

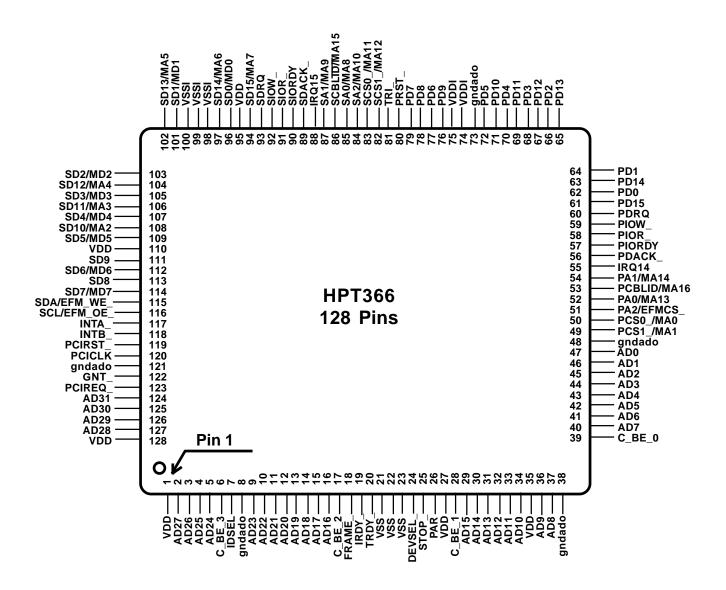

## 2.1 128 Pins Signal Descriptions

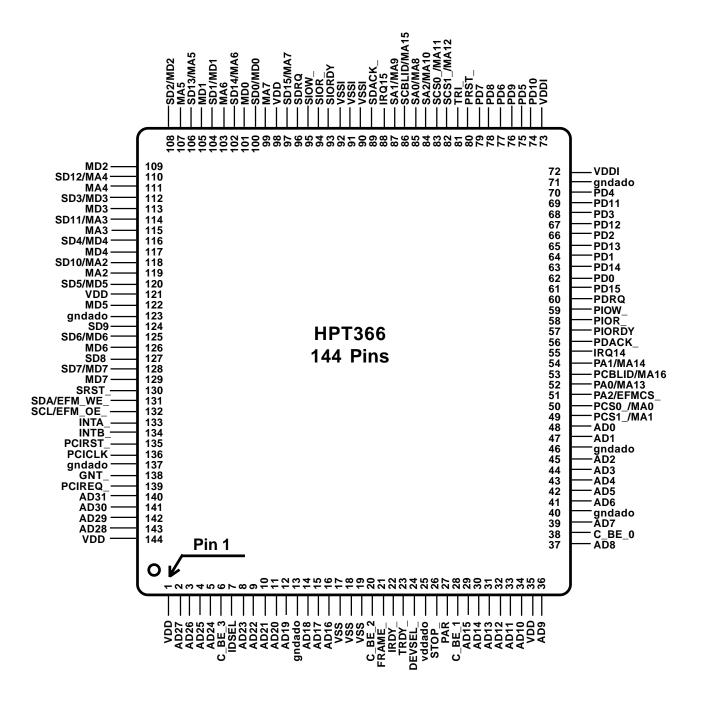

## 2.2 144 Pins Signal Descriptions

## 2.3 128 Pins Listing

## • System Pins

| Pin Number | Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                     |

|------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 120        | PCICLK   | ı    | Clock provides timing for all transactions on the PCI bus and is an input to every PCI device. All other PCI signals are sampled on the rising edge of CLK, and other timing parameters are defined with respect to this edge. Clock can optionally serve as the SCSI core clock, but this may effect Fast SCSI transfer rates. |

| 119        | PCIRST_  | I    | Reset PCI Bus                                                                                                                                                                                                                                                                                                                   |

#### Power and Ground Pins

| Pin Number             | Pin Name | Туре | Description                                         |

|------------------------|----------|------|-----------------------------------------------------|

| 21,22,23               | VSS      |      | Ground reference power supply IC, input and output. |

| 98,99,100              | VSSI     |      | Ground reference power supply onput, input and IC.  |

| 1,27,35,95,<br>110,128 | VDD      |      | Positive power supply output.                       |

| 74,75                  | VDDI     |      | Positive power supply output and IC.                |

| 8,38,48,<br>73,121     | gndado   |      | Ground Output                                       |

#### • Interface Control Pins

| Pin Number | Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | IDSEL    | I    | <b>Initialization Device Select</b> is used as a chip select in place of the upper 24 address lines during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                          |

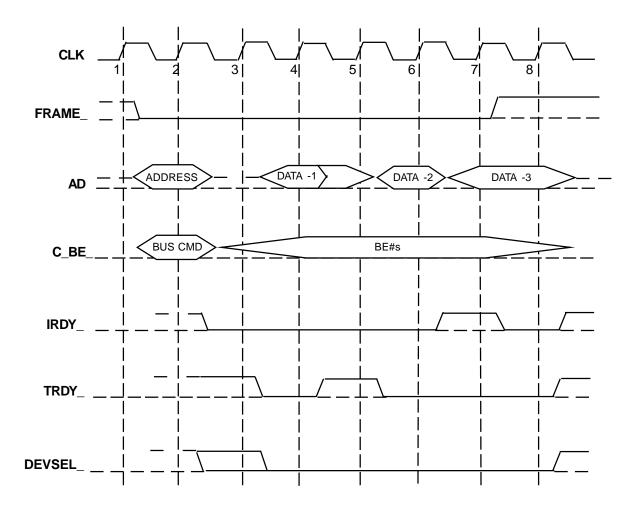

| 18         | FRAME_   | I/O  | <b>Cycle Frame</b> is driven by the current master to indicate the beginning and duration of an access. FRAME_ is asserted to indicate that a bus transaction is beginning. While FRAME_ is deasserted, either the transaction is in the final data phase or the bus is idle.                                                                                                                                                                                                                                                  |

| 19         | IRDY_    | I/O  | Initiator Ready indicates the initiating agents(bus masters) ability to complete the current data phase of the transaction. IRDY_ is used with TRDY_ A data phase is completed on any clock when both IRDY_ and TRDY_ sampled asserted. During a write, IRDY_ indicates that valid data is present on AD(31-0). During a read, it indicates that master is prepared to accept data. Wait cycles are inserted until both IRDY_ and TRDY_ are asserted together.                                                                 |

| 20         | TRDY_    | I/O  | Target Ready indicates the target agents (selected devices) ability to complete the current data phase of the transaction. TRDY_ is used with IRDY A data phase is completed on any clock when used with IRDY A data phase is completed on any clock when both TRDY_ and IRDY_ are sampled asserted. During a write, TRDY_ indicates that the target is prepared to accept data. During a read,it indicates that valid data is present on AD(31-0). Wait cycles are inserted until both IRDY_ and TRDY_ are asserted together. |

| 24         | DEVSEL_  | I/O  | <b>Device Select</b> indicates that the driving device has decoded its address as the target of the current access. As an input, it indicates to a master whether any device on the bus has been selected.                                                                                                                                                                                                                                                                                                                     |

| 25         | STOP_    | I/O  | <b>Stop</b> indicates that the selected target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Arbitration Pins

| Pin Number | Pin Name | Туре | Description                                                                                |

|------------|----------|------|--------------------------------------------------------------------------------------------|

| 123        | PCIREQ_  | 0    | <b>Request</b> indicates to the system arbiter that this agent desires use of the PCI bus. |

| 122        | GNT_     | I    | <b>Grant</b> indicates to the agent that access to the PCI bus has been granted.           |

## • PCI Interrupt Pins

| <br>Pin Number | Pin Name | Туре | Description                                                                                  |

|----------------|----------|------|----------------------------------------------------------------------------------------------|

| 117            | INTA_    | 0    | Interrupt A is used to request an interrupt.                                                 |

| 118            | INTB_    | 0    | Interrupt B is used to request an interrupt and only has meaning on a multi-function device. |

## Address/Data Pins

| Pin Number                                                                                                                 | Pin Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 124,125,126,<br>127,2,3,4,5,<br>9,10,11,12,<br>13,14,15,16,<br>29,30,31,32,<br>33,34,36,37,<br>40,41,42,43,<br>44,45,46,47 | AD(31-0)   | I/O  | Physical longword <b>Address and Data</b> are multiplexed on the same PCI pins. During the first clock of a transaction, AD (31-0) contain a physical byte address. During subsequent clocks, AD(31-0) contain data. A bus transaction consists of an address phase followed by one or more data phase. PCI supports both read and write bursts. AD(7-0) define the least significant byte, and AD(31-24) define the most significant byte. |

| 6,17,28,39                                                                                                                 | C_BE_(3-0) | I/O  | Bus <b>command and byte enables</b> are multiplexed on the same PCI pins. During the address phase of a transaction, C_BE_(3-0) define the bus command. During the data phase, C_BE_(3-0) are used as byte enables. The byte enables determine which byte lanes carry meaningful data. C_BE_0 applies to byte 0, and C_BE_3 to byte 3.                                                                                                      |

| 26                                                                                                                         | PAR        | I/O  | <b>Parity</b> is the even parity bit that protects the AD(31-0) and C_BE_(3-0) lines. During address phase, both the address and command bits are covered. During data phase, both data and byte enables are covered.                                                                                                                                                                                                                       |

#### • IDE Interface Pins

| Pin Number                                                                       | Pin Name             | Туре | Description                                                                             |

|----------------------------------------------------------------------------------|----------------------|------|-----------------------------------------------------------------------------------------|

| 84,87,85                                                                         | SA(2-0)/<br>MA(10-8) | 0    | Secondary IDE Device Address They are also used as Memory Address Bus signal.           |

| 94,97,102,<br>104,106,108,<br>111,113,114,<br>112,109,107,<br>105,103,101,<br>96 | SD(15-0)             | I/O  | Secondary IDE Data They are also used as Memory Data Bus and Memory Address Bus signal. |

| 89                                                                               | SDACK_               | 0    | Secondary IDE DMA Acknowledge                                                           |

| 56                                                                               | PDACK_               | 0    | Primary IDE DMA Acknowledge                                                             |

| 90                                                                               | SIORDY               | I    | Secondary IDE Channel I/O Ready                                                         |

| 57                                                                               | PIORDY               | I    | Primary IDE Channel I/O Ready                                                           |

| 93                                                                               | SDRQ                 | I    | Secondary IDE DMA Request                                                               |

| 60                                                                               | PDRQ                 | I    | Primary IDE DMA Request                                                                 |

| 61,63,65,67,<br>69,71,76,78,<br>79,77,72,70,<br>68,66,64,62                      | PD(15-0)             | I/O  | Primary IDE Data                                                                        |

| 51,54,52                                                                         | PA(2-0)              | 0    | Primary IDE Device Address They are also used as EFMCS_ and Memory address Bus signal.  |

## • EPROM Interface Pins

| Pin Number                                                             | Pin Name            | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53,86,54,52,<br>82,83,84,87,<br>85,94,97,102,<br>104,106,108,<br>49,50 | MA(16-0)            | 0    | Memory Address Bus. This bus is used in conjunction with the memory address strobe pins and external address latches to assemble up to a 20-bit address for an external EPROM or flash memory. This bus puts out the least significant byte first and finishes with the most significant bits. It is also used to write data to a flash memory or read data into the chip from external EPROM/flash memory. They are also use as PCBLID, SCBLID, PA(1-0), SCS1_, SCS0_, SA(2-0), SD(15-10), PCS1_ and PCS0_ signal. |

| 114,112,109,<br>107,105,103,<br>101,96                                 | SD(7-0)/<br>MD(7-0) | I/O  | Memory Data Bus. This bus is used in conjunction with the memory address strobe pins and external address latches to assemble up to a 20-bit address for an external EPROM or flash memory. This bus puts out the least significant byte first and finishes with the most significant bits. It is also used to write data to a flash memory or read data into the chip from external EPROM/flash memory. All MD pins have internal pull-down resistors. They are also used as Secondary IDE Data signal.            |

| 116                                                                    | SCL/<br>EFM_OE_     | 0    | EPROM Output Enable. This pin is used as an output enable signal to an external EPROM or flash memory during read operations. When system reset, this signal will be latched on rising edge of PCIRST_ signal. If the latched signal is high-LEV, IC will work at Disable Allocation mode. If the signal is low-LEV, IC will work at Enable Allocation mode. It is also used as a SCL signal.                                                                                                                       |

| 115                                                                    | SDA/<br>EFM_WE_     | I/O  | <b>EPROM Write Enable.</b> This pin is used as a write enable signal to an external flash memory. When system reset, this signal will be latched on rising edge of PCIRST_ signal. If latched values of SDA/EFM_WE_ & TRI signals are both high-LEV, the configuration will be loaded from parallel EPROM automatically. It is also used as a SDA signal.                                                                                                                                                           |

| 51                                                                     | PA2/<br>EFMCS_      | I/O  | <b>EPROM Chip Select.</b> It is also used as a Primary IDE Device Address signal.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## • Other Pins

| Pin Number | Pin Name   | Туре | Description                                                                                                                                                                                                                                                                                   |

|------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82         | SCS1_/MA12 | 0    | Secondary Device Chip Select 1.                                                                                                                                                                                                                                                               |

| 83         | SCS0_MA11  | 0    | Secondary Device Chip Select 0.                                                                                                                                                                                                                                                               |

| 49         | PCS1_/MA1  | 0    | Primary Device Chip Select 1.                                                                                                                                                                                                                                                                 |

| 50         | PCS0_/MA0  | 0    | Primary Device Chip Select 0.                                                                                                                                                                                                                                                                 |

| 88         | IRQ15      | I    | Interrupt Request 15. This pin is used to rquest an interrupt for secondary IDE port in PCI IDE Legacy Mode. (PC-AT compatible.)IRQ15 is tri-stated when IDE port 1 is in Native Mode.                                                                                                        |

| 55         | IRQ14      | I    | Interrupt Request 14. This pin is used to request an interrupt in PCI IDE Legacy Mode. (For PC-AT compatibles.) IRQ 14 is tri-stated when IDE port 0 is in Native Mode.                                                                                                                       |

| 91         | SIOR_      | 0    | Secondary I/O Read.                                                                                                                                                                                                                                                                           |

| 58         | PIOR_      | 0    | Primary I/O Read.                                                                                                                                                                                                                                                                             |

| 92         | SIOW_      | 0    | Secondary I/O Write.                                                                                                                                                                                                                                                                          |

| 59         | PIOW_      | 0    | Primary I/O Write.                                                                                                                                                                                                                                                                            |

| 80         | PRST_      | 0    | Primary Reset                                                                                                                                                                                                                                                                                 |

| 86         | SCBLID     | 0    | Secondary Cable Assembly Type Identifier.                                                                                                                                                                                                                                                     |

| 53         | PCBLID     | 0    | Primary Cable Assembly Type Identifier.                                                                                                                                                                                                                                                       |

| 81         | TRI        | 1    | When system reset, the TRI signal will be latched on rising edge of PCIRST_ signal. If the latched value of TRI is 0, the configuration will be loaded from serial EPROM automatically. When the system works normally and TRI signal is low-LEV, the outputs of ATA BUS are high- impedance. |

## 2.4 144 Pins Listing

## • System Pins

| Pin Number | Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                     |

|------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 136        | PCICLK   | I    | Clock provides timing for all transactions on the PCI bus and is an input to every PCI device. All other PCI signals are sampled on the rising edge of CLK, and other timing parameters are defined with respect to this edge. Clock can optionally serve as the SCSI core clock, but this may effect Fast SCSI transfer rates. |

| 135        | PCIRST_  | Ī    | Reset PCI Bus                                                                                                                                                                                                                                                                                                                   |

#### • Power and Ground Pins

| Pin Numbe               | Pin Name | Туре | Description                                         |

|-------------------------|----------|------|-----------------------------------------------------|

| 17,18,19                | VSS      |      | Ground reference power supply IC, input and output. |

| 90,91,92                | VSSI     |      | Ground reference power supply onput, input and IC.  |

| 1,25,35,<br>98,121,144  | VDD      |      | Positive power supply output.                       |

| 72,73                   | VDDI     |      | Positive power supply output and IC.                |

| 13,40,46,<br>71,123,137 | gndado   |      | Ground Output                                       |

#### • Interface Control Pins

| Pin Number | Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | IDSEL    | I    | <b>Initialization Device Select</b> is used as a chip select in place of the upper 24 address lines during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                          |

| 21         | FRAME_   | I/O  | <b>Cycle Frame</b> is driven by the current master to indicate the beginning and duration of an access. FRAME_ is asserted to indicate that a bus transaction is beginning. While FRAME_ is deasserted, either the transaction is in the final data phase or the bus is idle.                                                                                                                                                                                                                                                  |

| 22         | IRDY_    | I/O  | Initiator Ready indicates the initiating agents(bus masters) ability to complete the current data phase of the transaction. IRDY_ is used with TRDY_ A data phase is completed on any clock when both IRDY_ and TRDY_ sampled asserted. During a write, IRDY_ indicates that valid data is present on AD(31-0). During a read, it indicates that master is prepared to accept data. Wait cycles are inserted until both IRDY_ and TRDY_ are asserted together.                                                                 |

| 23         | TRDY_    | I/O  | Target Ready indicates the target agents (selected devices) ability to complete the current data phase of the transaction. TRDY_ is used with IRDY A data phase is completed on any clock when used with IRDY A data phase is completed on any clock when both TRDY_ and IRDY_ are sampled asserted. During a write, TRDY_ indicates that the target is prepared to accept data. During a read,it indicates that valid data is present on AD(31-0). Wait cycles are inserted until both IRDY_ and TRDY_ are asserted together. |

| 24         | DEVSEL_  | I/O  | <b>Device Select</b> indicates that the driving device has decoded its address as the target of the current access. As an input, it indicates to a master whether any device on the bus has been selected.                                                                                                                                                                                                                                                                                                                     |

| 26         | STOP_    | I/O  | <b>Stop</b> indicates that the selected target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Arbitration Pins

| Pin Number | Pin Name | Туре | Description                                                                                |

|------------|----------|------|--------------------------------------------------------------------------------------------|

| 139        | PCIREQ_  | 0    | <b>Request</b> indicates to the system arbiter that this agent desires use of the PCI bus. |

| 138        | GNT_     | I    | <b>Grant</b> indicates to the agent that access to the PCI bus has been granted.           |

## • PCI Interrupt Pins

| Pin Number | Pin Name | Туре | Description                                                                                  |

|------------|----------|------|----------------------------------------------------------------------------------------------|

| 133        | INTA_    | 0    | Interrupt A is used to request an interrupt.                                                 |

| 134        | INTB_    | 0    | Interrupt B is used to request an interrupt and only has meaning on a multi-function device. |

#### Address/Data Pins

| Pin Number                                                                                                                | Pin Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 140,141,142,<br>143,2,3,4,5,<br>8,9,10,11,12,<br>14,15,16,29,<br>30,31,32,33,<br>34,36,37,39,<br>41,42,43,44,<br>45,47,48 | AD(31-0)   | I/O  | Physical longword <b>Address and Data</b> are multiplexed on the same PCI pins. During the first clock of a transaction, AD(31-0) contain a physical byte address. During subsequent clocks, AD(31-0) contain data. A bus transaction consists of an address phase followed by one or more data phase. PCI supports both read and write bursts. AD(7-0) define the least significant byte, and AD(31-24) define the most significant byte. |

| 6,20,28,38                                                                                                                | C_BE_(3-0) | I/O  | <b>Bus command and byte enables</b> are multiplexed on the same PCI pins. During the address phase of a transaction, C_BE_(3-0) define the bus command. During the data phase, C_BE_(3-0) are used as byte enables. The byte enables determine which byte lanes carry meaningful data. C_BE_0 applies to byte 0, and C_BE_3 to byte 3.                                                                                                     |

| 27                                                                                                                        | PAR        | I/O  | <b>Parity</b> is the even parity bit that protects the AD(31-0) and C_BE_(3-0) lines. During address phase, both the address and command bits are covered. During data phase, both data and byte enables are covered.                                                                                                                                                                                                                      |

#### • IDE Interface Pins

| Pin Number                                                                         | Pin Name             | Type | Description                                                                            |

|------------------------------------------------------------------------------------|----------------------|------|----------------------------------------------------------------------------------------|

| 84,87,85                                                                           | SA(2-0)/<br>MA(10-8) | 0    | IDE Device Address                                                                     |

| 97,102,106,<br>110,114,118,<br>124,127,128,<br>125,120,116,<br>112,108,104,<br>100 | SD(15-0)             | I/O  | IDE Data They are also used as Memory Data Bus and Memory Address Bus signal.          |

| 89                                                                                 | SDACK_               | 0    | Secondary IDE DMA Acknowledge                                                          |

| 56                                                                                 | PDACK_               | 0    | Primary IDE DMA Acknowledge                                                            |

| 93                                                                                 | SIORDY               | I    | Secondary IDE Channel I/O Ready                                                        |

| 57                                                                                 | PIORDY               | I    | Primary IDE Channel I/O Ready                                                          |

| 96                                                                                 | SDRQ                 | ı    | Secondary IDE DMA Request                                                              |

| 60                                                                                 | PDRQ                 | I    | Primary IDE DMA Request                                                                |

| 61,63,65,67,<br>69,74,76,78,<br>79,77,75,70,<br>68,66,64,62                        | PD(15-0)             | I/O  | Primary IDE Data                                                                       |

| 51,54,52                                                                           | PA(2-0)              | 0    | Primary IDE Device Address Them are also used as EFMCS_ and Memory Address Bus signal. |

#### • EPROM Interface Pins

| Pin Number                                                                                             | Pin Name            | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53,86,54,52,<br>82,83,84,87,<br>85,97,99,102,<br>103,106,107,<br>110,111,114,<br>115,118,119,<br>49,50 | MA(16-0)            | 0    | Memory Address Bus. This bus is used in conjunction with the memory address strobe pins and external address latches to assemble up to a 20-bit address for an external EPROM or flash memory. This bus puts out the least significant byte first and finishes with the most significant bits. It is also used to write data to a flash memory or read data into the chip from external EPROM/flash memory. They are also use as PCBLID, SCBLID, PA(1-0), SCS1_,SCS0_,SA(2-0),SD(15-10), PCS1_ and PCS0_ signal. (Please refer to <b>Other Pins</b> for MA7.) |

| 129,128,126,<br>125,122,120,<br>117,116,113,<br>112,109,108,<br>105,104,101,<br>100                    | MD(7-0)/<br>SD(7-0) | I/O  | Memory Data Bus. This bus is used in conjunction with the memory address strobe pins and external address latches to assemble up to a 20-bit address for an external EPROM or flash memory. This bus puts out the least significant byte first and finishes with the most significant bits. It is also used to write data to a flash memory or read data into the chip from external EPROM/flash memory. All MD pins have internal pull-down resistors. They are also used Secondary IDE Data signal.                                                         |

| 132                                                                                                    | SCL/<br>EFM_OE_     | 0    | <b>EPROM Output Enable.</b> This pin is used as an output enable signal to an external EPROM or flash memory during read operations. It is also used as a SCL signal.                                                                                                                                                                                                                                                                                                                                                                                         |

| 131                                                                                                    | SDA/<br>EFM_WE_     | 0    | <b>EPROM Write Enable.</b> This pin is used as a write enable signal to an external flash memory. When system reset, this signal will be latched on rising edge of PCIRST_ signal. If latched values of SDA/EFM_WE_ & TRI signals are both high-LEV, the configuration will be loaded from parallel EPROM automatically. It is also used as a SDA signal.                                                                                                                                                                                                     |

| 51                                                                                                     | PA2/<br>EFMCS_      | 0    | <b>EPROM Chip Select.</b> It is also used as a Primary IDE Device Address signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## • Other Pins

| Pin Number | Pin Name    | Туре | Description                                                                                                                                                                                                                                                                                  |

|------------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82         | SCS1_/MA12  | 0    | Secondary Device Chip Select 1.                                                                                                                                                                                                                                                              |

| 83         | SCS0_/MA11  | 0    | Secondary Device Chip Select 0.                                                                                                                                                                                                                                                              |

| 49         | PCS1_/MA1   | 0    | Primary Device Chip Select 1.                                                                                                                                                                                                                                                                |

| 50         | PCS0_/MA0   | 0    | Primary Device Chip Select 0.                                                                                                                                                                                                                                                                |

| 88         | IRQ15       | I    | Interrupt Request 15. This pin is used to rquest an interrupt for secondary IDE port in PCI IDE Legacy Mode. (PC-AT compatible.) IRQ15 is tri-stated when IDE port 1 is in Native Mode.                                                                                                      |

| 55         | IRQ14       | I    | Interrupt Request 14. This pin is used to request an interrupt in PCI IDE Legacy Mode. (For PC-AT compatibles.) IRQ 14 is tri-stated when IDE port 0 is in Native Mode.                                                                                                                      |

| 94         | SIOR_       | 0    | Secondary I/O Read.                                                                                                                                                                                                                                                                          |

| 58         | PIOR_       | 0    | Primary I/O Read.                                                                                                                                                                                                                                                                            |

| 95         | SIOW_       | 0    | Secondary I/O Write.                                                                                                                                                                                                                                                                         |

| 59         | PIOW_       | 0    | Primary I/O Write.                                                                                                                                                                                                                                                                           |

| 80         | PRST_       | 0    | Primary Reset                                                                                                                                                                                                                                                                                |

| 130        | SRST_       | 0    | Secondary Reset                                                                                                                                                                                                                                                                              |

| 86         | SCBLID/MA5  | 0    | Secondary Cable Assembly Type Identifier.                                                                                                                                                                                                                                                    |

| 53         | PCBLID/MA16 | 0    | Primary Cable Assembly Type Identifier.                                                                                                                                                                                                                                                      |

| 81         | TRI         | 1    | When system reset, the TRI signal will be latched on rising edge of PCIRST_ signal. If the latched value of TRI is 0, the configuration will be loaded from serial EPROM automatically. When the system works normally and TRI signal is low-LEV, the outputs of ATA BUS are high-impedance. |

| 94         | MA7         | I/O  | When system reset, the MA7 signal will be latched on rising edge of PCIRST_ signal. If the value is 1, the IC is packaged of 144 Pins. The MA7 pin must have a external pull_up resistor (<5K).                                                                                              |

# Chapter 3 Registers

## Introduction

This chapter will introduction PCI Configuration Registers and I/O Space Registers. HPT366 have two functions.

## 3.1 Registers Listing

| NO. | NAME                             | PAGE | ATTRIBUTE         |

|-----|----------------------------------|------|-------------------|

| 1   | Vendor ID and Device ID          | 3-4  |                   |

| 2   | Command Register                 | 3-4  |                   |

| 3   | Status Register                  | 3-5  |                   |

| 4   | Revision Identification Register | 3-5  |                   |

| 5   | Class Code Register              | 3-6  |                   |

| 6   | Latency Timer Register           | 3-6  |                   |

| 7   | Header Type Register             | 3-7  | PCI Configuration |

| 8   | Command Block Register           | 3-7  | Registers         |

| 9   | Control Block Register           | 3-8  |                   |

| 10  | I/O Space Base Register          | 3-8  |                   |

| 11  | CardBus CIS Pointer Register     | 3-8  |                   |

| 12  | Subsystem Vendor ID Register     | 3-9  |                   |

| 13  | Subsystem ID Register            | 3-9  |                   |

| 14  | Expansion ROM Base Register      | 3-9  |                   |

| 15  | Interrupt Line Register          | 3-10 |                   |

| 16  | Interrupt Pin Register           | 3-10 |                   |

| NO. | NAME                                          | PAGE | ATTRIBUTE           |

|-----|-----------------------------------------------|------|---------------------|

| 17  | IDE Timing0 Register                          | 3-11 |                     |

| 18  | IDE Timing1 Register                          | 3-12 |                     |

| 19  | MISC.Control1 Register                        | 3-13 |                     |

| 20  | MISC.Control2 Register                        | 3-14 | PCI Configuration   |

| 21  | MISC.Control3 Register                        | 3-15 | Registers           |

| 22  | MISC.Control4 Register                        | 3-15 |                     |

| 23  | Bus Status1 Register                          | 3-16 |                     |

| 24  | Bus Status2 Register                          | 3-17 |                     |

| 25  | Cable Select Register                         | 3-17 |                     |

| 26  | Bus Master Command Register                   | 3-18 | I/O Space Registers |

| 27  | Bus Master Status Register                    | 3-18 |                     |

| 28  | Bus Master Scatter Gather Table Base Register | 3-19 |                     |

## 3.2 PCI Configuration Registers

The PCI Configuration registers are accessed by performing a configuration read/write to the device with its IDSEL pin asserted and the appropriate value in AD(10:8) during the address phase of the transaction. All PCI-compliant devices, must support the Vendor ID, Device ID, Command, and Status Registers. Support of other PCI-compliant registers is optional.

#### **Vendor ID and Device**

Address: 00h-03h

Attribute: Read Only/Power On Loading

| BIT   | DESCRIPTION                                        |

|-------|----------------------------------------------------|

| 31:16 | Device Identification Number:IDE Controller =0003h |

| 15:0  | Vendor Identification Number =1103h                |

\*Notes: These fields identify the manufacturer of the device and particular device.

#### **Command Register**

Address: 04h-05h Attribute: R/W

| BIT   | DESCRIPTION                                           |

|-------|-------------------------------------------------------|

| 15:10 | Reserved                                              |

| 9     | Fast Back-to-Back Enable(Not Implemented).Hardwired 0 |

| 8:3   | Reserved                                              |

| 2     | Bus Master Enable.If set 1,Master Mode Enable.        |

| 1     | Memory Space Enable.1=Enable.0=Disable.               |

| 0     | I/O Space Enable.1=Enable.0=Disable.                  |

#### **Status Register**

Address: 06h-07h Attribute: Read Only

| BIT   | DESCRIPTION                         |

|-------|-------------------------------------|

| 15:14 | Reserved                            |

| 13    | Master Abort.                       |

| 12    | Received Target Abort.              |

| 11    | Signaled Target Abort.              |

| 10:9  | DEVSEL_ Timing.Hardwired 01-Medium. |

| 8:0   | Reserved                            |

\*Notes: Reads to this register behave normally.

#### **Revision Identification Register**

Address: 08h

Attribute: Read Only/Power On Loading

| BIT | DESCRIPTION           |

|-----|-----------------------|

| 7:0 | Revision ID Byte=01h. |

\*Note: This field specifies device and revision identifiers.

#### **Class Code Register**

Address: 09h-0Bh

Attribute: Read Only/Power On Loading

| BIT  | DESCRIPTION                                                                  |

|------|------------------------------------------------------------------------------|

| 23:0 | If Compatible Mode:Class Code=010180h, If In Native Mode:Class Code=018000h. |

\*Notes: This register is used to identify the generic function of the device. The upper byte of this register is a base class code, the middle byte is a subclass code, and the lower byte identifies a specific register-level programming interface.

#### **Latency Timer Register**

Address:0Dh Attribute: R/W

| BIT | DESCRIPTION   |

|-----|---------------|

| 7:0 | Latency Timer |

\*Notes: The Latency Timer Register specifies, in units of PCI bus clocks, the value of the Latency Timer for this PCI bus master.

#### **Header Type Register**

Address: 0Eh

Attribute: Read Only

| BIT | DESCRIPTION      |

|-----|------------------|

| 7:0 | Header Type=80h. |

\*Notes: This register identifies whether or not the device contains multiple functions.

#### **Command Block Register**

Primary Channel: 10h-13h

Attribute: R/W

| BIT    | DESCRIPTION                                                                           |

|--------|---------------------------------------------------------------------------------------|

| 31 : 3 | Base registers used to map Command Block registers must ask for 8 bytes of I/O space. |

\*Notes: In mode the registers of the IDE channels are completely relocatable in I/O space. Base Address sters in the PCI IDE controller Configuration Space registers are used to map the IDE register into pace.

#### **Control Block Register**

Primary Channel: 14h-17h

Attribute: R/W

| BIT    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31 : 2 | Base Address Registers in the PCI IDE controller's Configuration Space Registers are used to map the IDE register into space. Base registers to map Control Block registers must ask for 4 bytes of I/O space. In this four-byte allocation the at offset 02h is where the Alternate Status/Device Control byte is location. Other bytes in the four-allocation(bytes at offset 0,1 and 3) are undefined and may be used for device specific purposes. |  |

#### I/O Space Base Register

Address: 20h-23h Attribute: R/W

| BIT  | DESCRIPTION       |

|------|-------------------|

| 31:8 | I/O Base Address. |

| 7:1  | Reserved.         |

| 0    | Hardwired to 1.   |

#### **CardBus CIS Pointer Register**

Address: 28h

Attribute: Read Only. Power On Loading

| Bit  | Description          |

|------|----------------------|

| 31:0 | CardBus CIS Pointer. |

#### **Subsystem Vendor ID Register**

Address: 2C-2Dh

Attribute: Read Only/Power On Loading

| BIT  | DESCRIPTION          |

|------|----------------------|

| 15:0 | Subsystem Vendor ID. |

#### **Subsystem ID Register**

Address: 2E-2Fh

Attribute: Read Only/Power On Loading

| BIT   | DESCRIPTION   |

|-------|---------------|

| 31:16 | Subsystem ID. |

#### **Expansion ROM Base Register**

Address: 30h-33h Attribute: R/W

| BIT   | DESCRIPTION           |

|-------|-----------------------|

| 31:17 | ROM Base Address      |

| 16:1  | Reserved              |

| 0     | Address decode enable |

\*Notes: This register handles the base address and size information for the expansion ROM. It functions exactly like the Base Address registers, except that the encoding of the bits is different.

The Expansion ROM Enable bit, bit 0, is the only bit defined in this register. This bit controls whether or not the device accepts accesses to its expansion ROM. When the bit is set, address decoding is enabled, and a device is used with or without an expansion ROM depending on the system configuratio. To access the external memory interface, also set the Memory Space bit in the Command register. It exists in function 0 only!

#### **Interrupt Line Register**

Address: 3Ch Attribute: R/W

| BIT | DESCRIPTION                            |

|-----|----------------------------------------|

| 7:0 | Interrupt Line Number.After Reset=00h. |

\*Notes: This register can communicate interrupt line routing information. POST software writes the routing information into this register as it configures the system. The value in this register tells which input of the system interrupt controller(s) the devices interrupt pin is connected to. Values in this register are specified by system architecture.

#### **Interrupt Pin Register**

Address: 3Dh

Attribute: Read Only, Power On Loading

| BIT | DESCRIPTION                                                                                                |

|-----|------------------------------------------------------------------------------------------------------------|

| 7:0 | Interrupt Pin Number.Hardwired to 1.Connected to INTA In the function 2, Hardwired to 2. Connected to INTB |

\*Notes: This register tells which interrupt pin the device uses. Its value is set to 01h for the Function A INTA\_ signal, and 02h for the Function B INTB\_ signal at power-up.

#### IDE Timing0 Register

Address: 40-43h Attribute: R/W

| BIT   | DESCRIPTION                             |

|-------|-----------------------------------------|

| 31    | Primary Drive 0 Buffer Enable. For PIO  |

| 30    | Primary Drive 0 PIO_MST Enable.         |

| 29    | Primary Drive 0 Normal DMA Enable.      |

| 28    | Primary Drive 0 udma Enable.            |

| 24:22 | Primary Drive 0 cmd_pre_high_time.      |

| 21:19 | Primary Drive 0 pre_high_time.          |

| 18:16 | Primary Drive 0 udma_cycle_time.        |

| 15:12 | Primary Drive 0 cmd_low_time.           |

| 11:8  | Primary Drive 0 cmd_high_time.          |

| 7:4   | Primary Drive 0 low time cycle number.  |

| 3:0   | Primary Drive 0 high time cycle number. |

## **IDE Timing1 Register**

Address: 44-47h Attribute: R/W

| BIT   | DESCRIPTION                             |

|-------|-----------------------------------------|

| 31    | Primary Drive 1 Buffer Enable. For PIO  |

| 30    | Primary Drive 1 PIO_MST Enable.         |

| 29    | Primary Drive 1 Normal DMA Enable.      |

| 28    | Primary Drive 1 udma Enable.            |

| 24:22 | Primary Drive 1 cmd_pre_high_time.      |

| 21:19 | Primary Drive 1 pre_high_time.          |

| 18:16 | Primary Drive 1 udma_cycle_time.        |

| 15:12 | Primary Drive 1 cmd_low_time.           |

| 11:8  | Primary Drive 1 cmd_high_time.          |

| 7:4   | Primary Drive 1 low time cycle number.  |

| 3:0   | Primary Drive 1 high time cycle number. |

### MISC.Control1 Register

Address: 50h Attribute: R/W

| ВІТ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Disable channel 1Block Read/Write Bit. 1=Disable Block Read/Write. 0=Enable Block Read/Write. After Reset this bit is 0. Software can set this bit by writing a 1 to it. It is cleared by writing a 0 to this bit. This bit is R/W.                                                                                                                                                                                        |

| 6   | Disable channel 0 Block Read/Write Bit. 1=Disable Block Read/Write. 0=Enable Block Read/Write. After Reset this bit is 0. Software can set this bit by writing a 1 to it. It is cleared by writing a 0 to this bit. This bit is R/W.                                                                                                                                                                                       |

| 5   | Secondary IDE channel enable Bit. 1=Enable,0=Disable. After reset this bit is set to 1. Software can disable this bit by writing a 0 to it.                                                                                                                                                                                                                                                                                |

| 4   | Primary IDE channel enable Bit.1=Enable,0=Disable. After reset this bit is set to 1.Software can disable this bit by writing a 0 to it.                                                                                                                                                                                                                                                                                    |

| 3   | Clear Buffer 1 Bit. 1=Clear Buffer. 0=Not Clear Buffer. Software clear buffer pointer and counter to 0 by writing this bit to 1. Clear Buffer Signal is one PCI clock Pulse only.                                                                                                                                                                                                                                          |

| 2   | Clear Buffer 0 Bit. 1=Clear Buffer. 0=Not Clear Buffer. Software clear buffer pointer and counter to 0 by writing this bit to 1. Clear Buffer Signal is one PCI clock Pulse only.                                                                                                                                                                                                                                          |

| 1   | Allocate Address 17x Enable Bit. 1=Enable,0=Disable. After Reset This bit is set to 0. If Dis_alc pin=0,hardware set this bit to 1 automatically. Enanble means that all Secondary IDE Device Registers are allocated to I/O. BA offset 0X18, 0X1C. This Bit=0 (Disable) means all Secondary IDE Registers are at Default IDE Address. This bit is Read Only. (Note:In two Functions, it not existing.)                    |

| 0   | Allocate Address 1Fx Enable Bit. 1=Enable,0=Disable. After Reset This bit is set to 0. If Dis_alc Pin=0,then hardware set this bit to 1 automatically. Enable means that all primary IDE Device Registers are allocated to I/O. BA OFFSET 0X10, 0X14. This Bit =0 (Disable) means all Primary IDE Registers are at Default IDE Address. This bit is Read Only. (Note: In Function second, it's adress is 170-177 and 376.) |

### MISC.Control2 Register

Address: 51h Attribute: R/W

| BIT | DESCRIPTION                                                                                                                                                                                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | Fast Interrupt Enable Bit. 1=enable,0=disable. If enable,Interrupt will be generated before IDE interrupt occur. After reset this bit is 0. R/W                                                            |

| 14  | Hold channel 1 Interrupt enable Bit. 1=enable,0=disable. If enable,when read from IDE interrupt will be generated after the buffer is empty. After reset this bit is 0. R/W                                |

| 13  | Hold channel 0 Interrupt enable Bit. 1=enable,0=disable. If enable,when read from IDE interrupt will be generated after the buffer is empty. After reset this bit is 0. R/W                                |

| 12  | Enable Clear SG bit. 0=Disable 1=Enable. When SG Counter is greater than IDE Transfer Size. If this bit is 1,Hardware will automatically Clear SG State Machine after Interrupt Asserted. This Bit is R/W. |

| 11  | Channel 1 Read Flush Bit. 0=Not Flush.1=Flush. Software Flush all Contents in FIFO by Writing a 1 to this bit. Flush is one PCI Clock Pulse.                                                               |

| 10  | Channel 0 Read Flush Bit. 0=Not Flush.1=Flush. Software Flush all Contents in FIFO by Writing a 1 to this bit. Flush is one PCI Clock Pulse.                                                               |

| 9   | Clear Bus Master State Machine Bit.0=Not Clear. 1=Clear. Software Clear Master State Machine by Writing a 1 to this bit. Clear Master State Machine is one PCI Clock Pulse.                                |